# Paper 1

by Prayadi Prayadi

**Submission date:** 10-Nov-2020 05:34AM (UTC+0700)

**Submission ID:** 1441268442

File name: n\_of\_4-digit\_Count-Up\_with\_7-segment\_5-Inch\_SM415001L\_Final.pdf (675.86K)

Word count: 3510

Character count: 16621

## Design of 4-digit Count-Up with 7-Segment 5-Inch SM415001L

Muhamm Prayadi Sulistyanto Politeknik Makatronika Sanata Dharma, Yogyakarta, Indonesia prayadi@pmsd.ac.id

Abstract- In daily life, we have encountered many 7segments uses. The 7-segment has been commonly used to display public information or the number of calculations (counters). A Control Decoder as a 7-segment driver, IC CMOS and TTL as the decoder controller, has also been widely marketed. Various methods are used to counter the final goal to find out the number of objects. In this research, the researchers performed a 4-digit count-up by using the CD4510B CMOS IC as a BCD Count-Up and CD4511B as a 5-inch BCD to 7-segment decoder SM415001L. The uses of CD4510B ICs as a BCD Up/Down counter can generate binary numbers, according to the results of the counter on pins Q1, Q2, Q3, and Q4. The IC CMOS CD4511B, which, according to the datasheet was intended for 7-segment common cathode, could also be used for 7-segment common anode drivers by adding logic inverting circuits using transistors BC547 and CD4511B CMOS IC, combined with a logic inverting circuit. The 7-segment 5Inch SM415001L could display Count-Up numbers from 0000 to

Keywords— 7-segment, BCD, Decoder, IC TTL, IC CMOS, Counting, CD4510B, CD4511B.

#### I. INTRODUCTION

The 7-segment sizes vary, ranging from 0.56 inches to a large size 5 inches. Various kinds of articles related to the use of 7-segment as a viewer are discussed a lot, like the article entitled "A Novel 7-Segment Digital Clock Implementation on FPGA", which discusses the use of 7-segment as a clock viewer generated by the Field-programmable gate arrays (FPGA) system [1]. Counter research was further carried out by Tatsuya Saeki et al. entitled "Digital Cell Counting Devices Integrated with a Single-Cell Array" using CMOS sensors combined with microcavity arrays to count the number of new cells [2]. It was also conducted by Philip P. et al. in his article entitled "EcoCount: A New Digital Approach to Environmental Data Recording". In that study, the researchers conducted a digital counter, namely the voice recognition method, and the Microsoft Speech Programmers Interface (API) application to listen to what the user said. The API allowed the software to record the user's voice and identified keywords if it matched with what was being recorded, and then the counter process would be carried out [3]. Alain Crouzil et al., in a study entitled "Automatic vehicle counting system for traffic monitoring", researched with a focus on processing images captured on camera and counting by utilizing motion detection at the entry and the exit of the counting zones. The study focused on processing vehicle images to transmit counting signals [4]. The other

research related to object calculation by utilizing image processing are carried out, such as parking area calculations [5], vehicle detection and vehicle number calculation with Feature-Based Classifier [6], vehicle detection for Unmanned Aerial Vehicle Images [7], and counters of motorbikes coming out of the parking lot [8]. Several other research that used 7-segment as displays are conventional 7-segment displays using diodes and transistors arranged in matrix [9], 7-segment display standards for Burmese numerals [10], introduction of 7 characters -segment [11,12,13], 7-segment character modification for Bangla [14], message writing with 7-segment [15], 7-segment control with PIC16F84 microcontroller [16], 7-segment control with AND logic gate, NAND, OR, NOT [17], 7-segment BCD Efficiency with MGDI Modified Gate Diffusion Input Technique) [18], making six-digit clock with four-digit 7-segment module [19], and four 7-segment units to form a large 7-segment with a single decoder [20].

Control Decoder as a 7-segment driver has been widely marketed. The most commonly found of it are IC CMOS and TTL as the decoder controller. One example of a TTL decoder IC is 74LS247, with a maximum power supply voltage of 5.25 volts [21]. The most frequently used IC CMOS decoder and will be used in this study is the CD4511B, able to handle an 18-volt power supply voltage [22]. The reason for the use of IC CMOS CD4511B in this study is that each segment of the 7-segment common anode has 5 inches size with 2.5 volts [23]. The recommended voltage is 16 volts for one 7-segment [24].

Based on the literature study, a counter utilizing a 7-segment 5 inch and CMOS CD4511B decoder has not been found. In this study, the researchers performed a 4-digit count-up by utilizing the CMOS IC CD4510B as a BCD Count-Up and the CD4511B as a BCD to 7-segment 5 Inch decoder B415001L.

#### II. DESIGN BCD COUNT-UP 4 DIGITS

Count-Up with 7-segment 5 Inch SM415001L conducted in this study used a BCD up/down counter IC CMOS CD4510B. The use of IC CMOS CD 4510B was due to the suitability of the IC type (both CMOS) and the same power supply voltage that had a max supply voltage of 18 volts. The CD4510B CMOS IC could support both Count-Up and Count-Down, determined by the logic value, entered at pin 10(U/D). If the U/D pin had logic High, the CMOS IC CD4510B would run as a count-up counter, but if U/D had

Journal Email: jrc@umy.ac.id

logic Low, the CD4510B would work as a count-down counter. Pin 9 was used to reset the IC CD4510B counter, which would be active if it got logic High. The IC CD4510B also supported parallel inputs, namely A1, A2, A3, and A4, and the activation of the parallel inputs was controlled by pin 1 (PE). If PE accepted High input, the input parcel would be active. Counter activation was determined by pin 5 (CI). If CI had logic Low, the Clock Input would be active, and if CI had logic High, the counter would stop working [25].

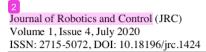

Figure 1 illustrates the 4-digit BCD Count-Up electronic circuit. The CMOS CD4510B IC serves as a Count-Up. The U/D has logic High, and the parallel input is deactivated by PE, given logic Low. Additionally, the clock input must be activated by giving logic Low to pin 5 (CI).

Fig. 1. 4-digit BCD Count-Up Design

Figure 1 shows the Input Clock (Pin. 15), which is an active-high circuit, a Pull-down resistor installed with  $10~\mathrm{K}\Omega$ . The purpose of installing a Pull-down resistor was to prevent the IC pin to float, i.e. always got logic Low [26]. In the Reset (Pin. 9), a highly active circuit, a pull-down resistor is installed. Table 1 and Table 2 present the test results of 4-digit BCD Count-Up circuits with a 12 volts Direct Current (DC). Paul Nicholls wrote on the website "www.pfnicholls.com", reviewing the use and the limitations of the IC CMOS 4510 counters [27]. In this research, the Count-Up design was not much different from what he did. The difference was that the clock was made using a switch as an

input, and the CO was used as the input clock (CI) of the CMOS IC CD4510B.

TABLE I. TEST RESULTS OF A 4-DIGIT BCD COUNT-UP SERIES

| Key P       | Key Presses |    | BCD 1 |    |    |    | BCD 2 |    |    |  |

|-------------|-------------|----|-------|----|----|----|-------|----|----|--|

| Count<br>Up | Reset       | Q1 | Q2    | Q3 | Q4 | Q1 | Q2    | Q3 | Q4 |  |

|             | 1           | 0  | 0     | 0  | 0  | 0  | 0     | 0  | 0  |  |

| 1           |             | 1  | 0     | 0  | 0  | 0  | 0     | 0  | 0  |  |

| 2           |             | 0  | 1     | 0  | 0  | 0  | 0     | 0  | 0  |  |

| 3           |             | 1  | 1     | 0  | 0  | 0  | 0     | 0  | 0  |  |

| 4           |             | 0  | 0     | 1  | 0  | 0  | 0     | 0  | 0  |  |

| 5           |             | 1  | 0     | 1  | 0  | 0  | 0     | 0  | 0  |  |

| 6           |             | 0  | 1     | 1  | 0  | 0  | 0     | 0  | 0  |  |

| 7           |             | 1  | 1     | 1  | 0  | 0  | 0     | 0  | 0  |  |

| 8           |             | 0  | 0     | 0  | 1  | 0  | 0     | 0  | 0  |  |

| 9           |             | 1  | 0     | 0  | 1  | 0  | 0     | 0  | 0  |  |

| 10          |             | 0  | 0     | 0  | 0  | 1  | 0     | 0  | 0  |  |

| 11          |             | 1  | 0     | 0  | 0  | 1  | 0     | 0  | 0  |  |

| 12          |             | 0  | 1     | 0  | 0  | 1  | 0     | 0  | 0  |  |

| 99          |             | 1  | 0     | 0  | 1  | 1  | 0     | 0  | 1  |  |

TABLE II. TEST RESULTS OF A 4-DIGIT BCD COUNT-UP SERIES

| Key Pro     | Key Presses |    | BCD 3 |    |    |    | BCD 4 |    |    |  |

|-------------|-------------|----|-------|----|----|----|-------|----|----|--|

| Count<br>Up | Reset       | Q1 | Q2    | Q3 | Q4 | Q1 | Q2    | Q3 | Q4 |  |

| 100         |             | 1  | 0     | 0  | 0  | 0  | 0     | 0  | 0  |  |

| 101         |             | 1  | 0     | 0  | 0  | 0  | 0     | 0  | 0  |  |

| 102         |             | 1  | 0     | 0  | 0  | 0  | 0     | 0  | 0  |  |

| 103         |             | 1  | 0     | 0  | 0  | 0  | 0     | 0  | 0  |  |

| 999         |             | 1  | 0     | 0  | 1  | 0  | 0     | 0  | 0  |  |

| 1000        |             | 0  | 0     | 0  | 0  | 1  | 0     | 0  | 0  |  |

| 1001        |             | 0  | 0     | 0  | 0  | 1  | 0     | 0  | 0  |  |

| 1002        |             | 0  | 0     | 0  | 0  | 1  | 0     | 0  | 0  |  |

| 1003        |             | 0  | 0     | 0  | 0  | 1  | 0     | 0  | 0  |  |

| 9999        |             | 1  | 0     | 0  | 1  | 1  | 0     | 0  | 1  |  |

| 10000       |             | 0  | 0     | 0  | 0  | 0  | 0     | 0  | 0  |  |

Table I and Table II show that the 4-digit BCD Count-Ip circuit can work as expected. The CD4510B CMOS IC output could perform at pins Q1, Q2, Q3, and Q4, which were binary combinations. When the counter reached 10, the Carry Out pin would output logic High and be used as an input clock on the next CD4510B IC. The BCD Count-Up testing was carried out by pressing up to 10000 times the input, and when the input reached 10000, the BCD 1 to BCD 4 showed binary zero.

#### III. DESIGN BCD TO 7-SEGMENT DECODER DRIVERS

The decoder driver from the BCD to 7-segment was designed using IC CMOS CD4511B, a common cathode 7-  $^{-1}$

segment decoder. There were four BCD input pins, seven output pins, and three operating pins. The three operation pins were LT (lamp test), BL (blinking), and LE (latch enable). The LT was located on pin 3, used to check each 7-segment lamp segment. By giving a logic Low, the IC CD4511B output, namely QA-QG, generated logic High so that all segments of the 7-segment common cathode would light up. The BL was located on pin 4, used to turn off all the 7-segment segments. If it received logic Low, the output QA-QG would issue logic Low, and in other words, the 7-segment common cathode would not turn on. The LE on pin 5 was used to lock the output QA - QG. When LE received high input, the output QA-QG would be maintained even though the BCD input changed.

In this research, the researchers utilized an IC CMOS CD4511B for the 7-segment 5-Inch SM415001L common anode [28]. A logic inverting driver was necessitated so that when IC CD4511B outputs logic High output, the 7-segment 5-Inch SM415001L turned on so that a transistor type BC547 was installed as a logic inverting driver.

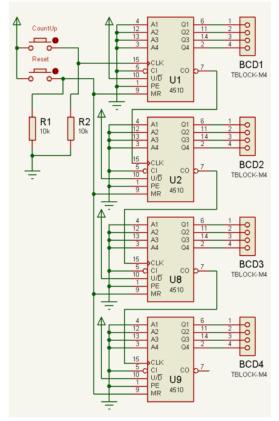

The design of BCD to 7-segment Decoder Driver with logic inverting and 7-segment SM415001L can be seen in Figure 2 and the results of BCD to 7-segment Decoder Driver Testing with logic inverting and 7-segment SM415001L with a Vcc voltage of 12 volts is shown in table II.

Fig. 2. Design BCD to 7-segment Decoder Drivers with logic inverting and 7-segment 5-Inch SM415001L

Figure 2 shows that the utilization of the transistor BC547 with the current at the base foot (IB) is a maximum of 200mA [29] so that the resistor is mounted as a current limiter of 4700  $\Omega$  (ohms). The current flowing can be calculated following Ohm's law, which is the magnitude of the voltage divided by resistance [30], resulting in the current flowing to the base foot that is 2.55mA, and make the transistor BC547 active and the 7-segment light up.

TABLE III. TESTING RESULTS OF BCD TO 7-SEGMENT DECODER

DRIVERS WITH LOGIC INVERTING AND 7-SEGMENT 5-INCH SM415001L

| INPUT BCD |   |              |   |    | SM4<br>1500 |    |    |    |    |    |    |

|-----------|---|--------------|---|----|-------------|----|----|----|----|----|----|

| A         | В | $\mathbf{c}$ | D | Qa | Qb          | Qc | Qd | Qe | Qf | Qg | 1L |

| 0         | 0 | 0            | 0 | 1  | 1           | 1  | 1  | 1  | 1  | 0  |    |

| 1         | 0 | 0            | 0 | 0  | 1           | 1  | 0  | 0  | 0  | 0  |    |

| 0         | 1 | 0            | 0 | 1  | 1           | 0  | 1  | 1  | 0  | 1  | 2  |

| 1         | 1 | 0            | 0 | 1  | 1           | 1  | 1  | 0  | 0  | 1  | 3  |

| 0         | 0 | 1            | 0 | 0  | 1           | 1  | 0  | 0  | 1  | 1  | 4  |

| 1         | 0 | 1            | 0 | 1  | 0           | 1  | 1  | 0  | 1  | 1  | 5  |

| 0         | 1 | 1            | 0 | 0  | 0           | 1  | 1  | 1  | 1  | 1  | Ь  |

| 1         | 1 | 1            | 0 | 1  | 1           | 1  | 0  | 0  | 0  | 0  |    |

| 0         | 0 | 0            | 1 | 1  | 1           | 1  | 1  | 1  | 1  | 1  | 8  |

| 1         | 0 | 0            | 1 | 1  | 1           | 1  | 0  | 0  | 1  | 1  | 9  |

Table III displays the test results of BCD to the 7-segment decoder and 7-segment 5-Inch SM415001L. It proves that the BCD to 7-segment decoder and the logic inverting driver can run well and that the 7-segment 5-Inch SM415001L can display the results of the decoder running properly, as expected.

### IV. RESULTS AND DISCUSSION

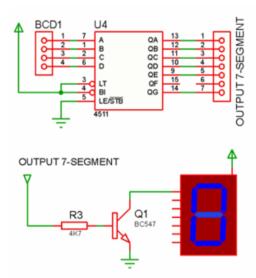

Figure 3 shows the results of the implementation of the 4-digit BCD Count-Up and BCD to the 7-segment Decoder Drivers. The pairing of the BC547 transistor was directly integrated with the 7-segment 5-Inch SM415001L and not on PCB. The power supply was 12Vdc, 2 Amperes, and the 4-digit count up with 7-segment 5-Inch SM415001L can light up, as shown in Figure 4.

Fig. 3. BCD Count-Up 4 Digit and BCD to 7-segment Decoder Drivers

Figure 4 illustrates that when the 4-digit Count-Up with 7-segment 5-Inch SM415001L displays the number "6609", it looks a little strange. The strangeness occurs because the shape of the number 6 (six) and number 9 (nine) is not like what we encounter every day, and the difference is presented in table IV.

Fig. 4. 4-Digit Count-Up with 7-segment 5-Inch SM415001L

| TABLE IV.     | COMPARISON OF SIX AND NINE N                            | UMBERS DISPLAYED |

|---------------|---------------------------------------------------------|------------------|

| I.Description | 4-Digit Count-Up with 7-<br>segment 5-Inch<br>SM415001L | daily life       |

| 6 (six)       | Ь                                                       | 5                |

| 9 (nine)      | 9                                                       | 9                |

#### II. CONCLUSION

The conclusion drawn from the research is that the counter works satisfactorily. The suitability of IC using CMOS IC type makes it easy to choose power supply and is easily adjusted to the voltage needed by the 7-segment. The use of IC CD4510B as a BCD Up/Down counter can produce binary numbers according to the results of the counter on pins Q1, Q2, Q3, and Q4. The IC CMOS CD4511B, according to the datasheet, is intended for 7-segment common cathodes can also be used for 7-segment driver common anode by adding a logic inverting circuit that uses a BC547 transistor and a CD4511B CMOS IC, combined with a logic inverting circuit. The 7-segment 5-inch SM415001L can display countup numbers from 0000 to 9999

#### ACKNOWLEDGMENT

This research was financially supported by Sanata Dharma Foundation. The author thanks the Director of Politeknik Makatronika Sanata Dharma and Innovatin Center Politeknik Mekatronika Sanata Dharma for some discussions.

#### REFERENCES

- [1] N. K. Vuthuri, V. Mahewar, G. Yeddluri, E. S. Movva, and V. Ch, "A novel 7-segment digital clock implementation on FPGA," in 2017 International Conference on Trends in Electronics and Informatics (ICEI), 2017, pp. 465–468, doi: 10.1109/ICOEI.2017.8300970.

- [2] T. Saeki, M. Hosokawa, T. K. Lim, M. Harada, T. Matsunaga, and T. Tanaka, "Digital cell counting device integrated with a single-cell

- array," PLoS One, vol. 9, no. 2, 2014, doi: 10.1371/journal.pone.0089011.

- P. P. Allen and N. Sewell, "EcoCount," SAGE Open, vol. 4, no. 2, p. 215824401453750, Jun. 2014, doi: 10.1177/2158244014537500.

- [4] A. Crouzil, L. Khoudour, P. Valiere, and N. Truong, "Automatic Vehicle Counting System for Traffic Monitoring," J. Electron. Imaging, vol. 25, p. 51207, Jun. 2016, doi: 10.1117/1JEL25.5.051207.

- [5] H. Zhou, L. Wei, M. Fielding, D. Creighton, S. Deshpande, and S. Nahavandi, "Car park occupancy analysis using UAV images," in 2017 IEEE International Conference on Systems, Man, and Cybernetics (SMC), 2017, pp. 3261–3265, doi: 10.1109/SMC.2017.8123131.

- [6] S. Choudhury, S. P. Chattopadhyay, and T. K. Hazra, "Vehicle detection and counting using haar feature-based classifier," in 2017 8th Annual Industrial Automation and Electromechanical Engineering Conference (IEMECON), 2017, pp. 106–109, doi: 10.1109/IEMECON.2017.8079571.

- [7] T. Moranduzzo and F. Melgani, "Automatic Car Counting Method for Ummanned Aerial Vehicle Images," IEEE Trans. Geosci. Remote Sens., vol. 52, no. 3, pp. 1635–1647, 2014, doi: 10.1109/TGRS.2013.2253108.

- [8] C. Chung, I. Chung, Y. Wang, and C. Chang, "The parking service quality and management: Digital image processing application for motorcycle counting," in 2015 International Conference on Machine Learning and Cybernetics (ICMLC), 2015, vol. 2, pp. 777–782, doi: 10.1109/ICMLC.2015.7340653.

- [9] R. K. Sharma, "A low-cost seven-segmented display system," Radio Electron. Eng., vol. 41, no. 5, pp. 223–224, 1971, doi: 10.1049/ree.1971.0063.

- [10] R. Karri and A. Orailoglu, "Standard seven segmented display for Burmese numerals," IEEE Trans. Consum. Electron., vol. 36, no. 4, pp. 959–961, 1990, doi: 10.1109/30.61581.

- [11] M. M. Hasan, A. Rahaman, M. M. S. Maswood, and M. M. Rahman, "An improved method for 7-segment numeric character recognition," in 2013 International Conference on Informatics, Electronics and Vision (ICIEV), 2013, pp. 1–6, doi: 10.1109/ICIEV.2013.6572607.

- [12] S. Popayorm, T. Titijaroonroj, T. Phoka, and W. Massagram, "Seven Segment Display Detection and Recognition using Predefined HSV Color Slicing Technique," in 2019 16th International Joint Conference on Computer Science and Software Engineering (JCSSE), 2019, pp. 224–229, doi: 10.1109/JCSSE.2019.8864189.

- [13] P. H. Kulkarni and P. D. Kute, "Optical numeral recognition algorithm for seven segment display," in 2016 Conference on Advances in Signal Processing (CASP), 2016, pp. 397–401, doi: 10.1109/CASP.2016.7746203.

- [14] M. M. Islam, M. K. Hossain, K. S. Hasan, and A. L. Haque, "A 7-segment display for Bangla, english and other Indian numerals," in 2008 International Conference on Electrical and Computer Engineering, 2008, pp. 631–635, doi: 10.1109/ICECE.2008.4769286.

- [15] S. G. Kennedy, "Writing messages on 7-segment displays," Electron. Syst. News, vol. 1988, no. 2, pp. 6–9, 1988, doi: 10.1049/esn.1988.0021.

- [16] P. Gardiner, "Driving 7-segment displays using PICs," Electron. Educ., vol. 2003, no. 3, pp. 19–21, 2003, doi: 10.1049/ee.2003.0032.

- [17] A. N. Borodzhieva, I. I. Stoev, and V. A. Mutkov, "FPGA Implementation of Code Converters of Decimal Digits from BCD Codes to Seven-Segment Display Code," in 2019 X National

- Conference with International Participation (ELECTRONICA), 2019, pp. 1–4, doi: 10.1109/ELECTRONICA.2019.8825588.

- [18] N. Radha and M. Maheswari, "An Efficient Implementation of BCD to Seven Segment Decoder using MGDI," in 2018 2nd International Conference on I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC)I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC), 2018 2nd International Conference on, 2018, pp. 475–479, doi: 10.1109/I-SMAC.2018.8653674.

- [19] H. Wan-Fu, "The design of a six-digit digital clock with a four-digit seven-segment display module," in 2011 International Conference on Electrical and Control Engineering, 2011, pp. 2656–2659, doi: 10.1109/ICECENG.2011.6058086.

- [20] A. Noore, "Single chip decoder design for large numeric displays," IEEE Trans. Consum. Electron., vol. 37, no. 4, pp. 844–847, 1991, doi: 10.1109/30.106948.

- [21] Z. Kaisheng and G. Guofa, "Design of Intellectualized Paper-pulp Measurement Management System," in 2009 Second Pacific-Asia Conference on Web Mining and Web-based Application, 2009, pp. 263–266.

- [22] X. Wang, T. Zheng, and Z. Zhang, "Design and Implementation of Intelligent Vehicle Control System Based on ROS," in 2018 Chinese Automation Congress (CAC), 2018, pp. 1661–1665.

- [23] L. J. da S. Moreira, C. C. Dias, R. B. C. Lima, P. R. Barros, and G. Acioli, "Modeling and control of a XY positioning table," in 2016 12th IEEE International Conference on Industry Applications (INDUSCON), 2016, pp. 1–6.

- [24] M. Jones and M. Joordens, "Design of an angular radial robotic stingray," in 2014 World Automation Congress (WAC), 2014, pp. 234–239.

- [25] T. Malatinec, V. Popelka, M. Huba, and P. Hudacko, "Laboratory model helicopter control using a lowcost Arduino hardware," in Proceedings of the 2014 15th International Carpathian Control Conference (ICCC), 2014, pp. 326–331.

- [26] V. Dubey, N. Dubey, and S. S. Chouhan, "Wireless Sensor Network Based Remote Irrigation Control System and Automation Using DTMF Code," in 2011 International Conference on Communication Systems and Network Technologies, 2011, pp. 34–37.

- [27] V. Ahmed and S. A. Ladhake, "Design of Ultra Low Cost Cell Phone Based Embedded System for Irrigation," in 2010 International Conference on Machine Vision and Human-machine Interface, 2010, pp. 718–721.

- [28] N. Jagtap, J. Wadgaonkar, and K. Bhole, "Smart wrist watch," in 2016 IEEE Students' Conference on Electrical, Electronics and Computer Science (SCEECS), 2016, pp. 1–6.

- [29] L. J. da S. Moreira, C. C. Dias, R. B. C. Lima, P. R. Barros, and G. Acioli, "Modeling and control of a XY positioning table," in 2016 12th IEEE International Conference on Industry Applications (INDUSCON), 2016, pp. 1–6.

- [30] M. S. Mannan and M. N. Sakib, "GSM based remote device controller using SIM548C," in Fifth International Conference on Computing, Communications and Networking Technologies (ICCCNT), 2014, pp. 1–4.

| Paper | 1 |

|-------|---|

|-------|---|

#### **ORIGINALITY REPORT**

7% SIMILARITY INDEX

6%

2%

2%

INTERNET SOURCES

**PUBLICATIONS**

STUDENT PAPERS

#### **PRIMARY SOURCES**

sintadev.ristekdikti.go.id

3%

Submitted to Higher Education Commission Pakistan

2%

Student Paper

www.nbp.com.pl

1%

Internet Source

<1%

4 mafiadoc.com

Internet Source

Lecture Notes in Electrical Engineering, 2016.

Publication

Publication

5

<1%

Dian Artanto, M. Prayadi Sulistyanto, Ign.

Deradjad Pranowo, Ervan Erry Pramesta.

"Drowsiness detection system based on eyeclosure using a low-cost EMG and ESP8266",

2017 2nd International conferences on

Information Technology, Information Systems

and Electrical Engineering (ICITISEE), 2017

1 %

Exclude quotes On Exclude matches < 6 words

Exclude bibliography On